文中资料来源:百度百科、HDMI详解

今天因为某条Hdmi线有问题,使用测试仪对Hdmi线测试以后发现是其中一芯断路了,鉴于之前一直没有认真了解过其原理,也正好借着这次好好了解了一下Hdmi的相关知识

HDMI,全称为(High Definition Multimedia Interface)高清多媒体接口,主要用于传输高清音视频信号。

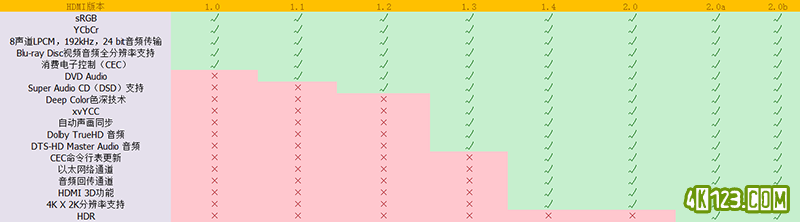

一、版本

目前Hdmi主要有以下版本:

HDMI 1.0

最早的HDMI 1.0版本于2002年12月推出,它的最大特点就是整合了音频流的数字接口,与当时PC界面中很流行的DVI接口相比,它更先进,更方便。HDMI 1.0版本支持从DVD到蓝光格式的视频流,而且具备CEC(consumer electronics control)功能,也就是在应用中,可以在所有连接设备间形成一种共通的联络,对设备组具备更方便的控制。

HDMI 1.1

2004年5月,HDMI 1.1版本面试。新增对DVD音频的支持。

HDMI 1.2

HDMI1.2版本于2005年8月推出,很大程度上解决了HDMI 1.1支持的分辨率较低、同电脑设备兼容性较差等问题。1.2版像素时钟运行频率达到165MHz,数据量达到4.95 Gbps,因此可以实现1080P。可以认为1.2版解决的是电视的1080P和电脑的点对点问题。

HDMI 1.3

2006年6月HDMI 1.3更新,带来最大的变化是将单链接带宽频率提升到340MHz,也就能让这些液晶电视获得10.2Gbps的数据传输量,1.3版的线是有4对传输通道组成,其中1对通道是时钟通道,另外3对是TMDS通道(最小化传输差分信号),他们的传输速度分别为3.4GBPS。那么3对就是3*3.4=10.2GPBS更是能将HDMI1.1、1.2版本所支持的24位色深大幅扩充至30位、36位及48位(RGB或YCbCr)。HDMI 1.3支持1080P;一些要求不高的3D也支持(理论上不支持,实际有些可以)。

HDMI 1.4

HDMI 1.4版本已经可以支持4K了,但是受制于带宽10.2Gbps,最高只能达到3840×2160分辨率和30FPS帧率。

HDMI 2.0

HDMI 2.0的带宽扩充到了18Gbps,支持即插即用和热插拔,支持3840×2160分辨率和50FPS、60FPS帧率。同时在音频方面支持最多32个声道,以及最高1536kHz采样率。HDMI 2.0并没有定义新的数据线和接头、接口,因此能保持对HDMI 1.x的完美向下兼容,现有的二类数据线可直接使用。HDMI 2.0并不会取代HDMI 1.x,而是基于后者的增强,任何设备要想支持HDMI 2.0必须首先保证对HDMI 1.x的基础性支持。

HDMI 2.0a

HDMI 2.0a的变化并不大,它的主要更新只有一个地方,那就是加入了对HDR格式传输的支持,能够显著增强图像质量。

HDMI 2.0b

HDMI2.0b兼容所有HDMI之前的规格版本,与HDMI2.0a并没有太大区别,HDMI2.0b也是目前为止HDMI最新的版本。 (所以网上说的HDMI2.0a比HDMI2.0b新并不对。HDMI官方的信息是2.0b为目前最新的接口版本)

HDMI 2.1

HDMI 2.1根据飞利浦撰写的白皮书增加支持“动态元” 简而言之:“HDMI 2.0A涵盖HDR EOTF信令和静态元数据元数据的动态是HDMI 2.1所涵盖。” 2017年1月4日提出 带宽提升至48Gbps 支持4K 120Hz及8K 60Hz 支持高动态范围成像(HDR),可以针对场景或帧数进行优化 支持eARC功能 可针对游戏帧数进行信号同步,减少画面撕裂 向后兼容HDMI 2.0、HDMI 1.4

二、Hdmi信号的传输

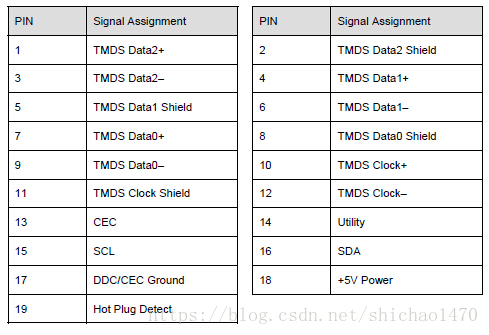

1. HDMI引脚: HDMI有A,B,C,D,E五种引脚类型,目前市面中比较常见的就是Type A:

其中

1-9 都是TMDS数据传输实际上用到的引脚,分为0,1,2三组

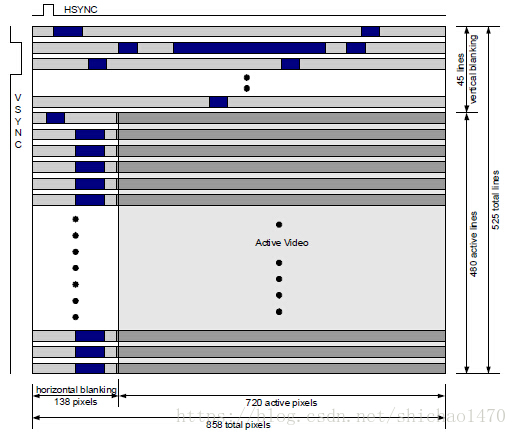

10-12 为TMDS时钟信号,如当前Video Timing为480p@60Hz(Htotal:800,Vtotal:525),则TMDS clock = 800x525x60 = 25.2MHz。TMDS clock就像是对像素的打包,一个clock分别在三个Channel传输一个像素的R、G、B(8bit)信号。

13 为CEC(consumer electronic control)类似一种扩展的HDMI功能,供厂家自己定制HDMI消息,(比如说你有一台sony的DVD与TV,两者用HDMI线接上,如果你用TV的遥控器可以控制DVD,另DVD执行某种功能,那么该功能的命令信号就是通过TV与DVD间的CEC引脚传输的)

14 为保留引脚,未使用(或者也可以为CEC提供多一个引脚)

15-16 为I2C引脚,用于DDC(Display Data Channel,主要用于EDID与HDCP的传输)传输。在HDMI的流程中,DDC通信几乎是最先做的(前有Hotplug),因为HDMI的主从两个设备需要通过DDC来获得他们对方设备的EDID,从而得到各种信息,并且通过比较timming以确定以后送出来的timming为最合适的

17 为接地引脚

18 为5v的AC引脚

19 为Hotplug(热拔插)引脚(用于监测HDMI设备有没有存在,如果存在(Hotplug为high)那么可以通过DDC去读EDID),HDMI有规定在HDMI 5vAC断电时source device可以读reciever device的EDID,也就是需要Hotplug为High。其中有两种Hotplug相关的情况会导致HDMI被识别为DVI: Hotplug为High,不过EDID并没有准备好,那么信号源设备会由于无法读到EDID而认为接收设备为DVI,这样会导致HDMI有图像无声的问题。 Hotplug为Low,也会导致信号源无法读到EDID而认为接收设备为DVI,从而导致HDMI有图无声 在TV这种有多个HDMI通道的情况下,有时会在多个HDMI通道进行切换,切换后HDMI通道应当先初始化,即先把Hotplug拉低,通知HDMI source device之前所用的EDID已经改变,需要重新读取,那么source device在Hotplug被拉高的时候会去读取新的EDID,但是拉低这个过程至少需要100ms,否则source device有可能不会去读取新的EDID,从而输出DVI信号

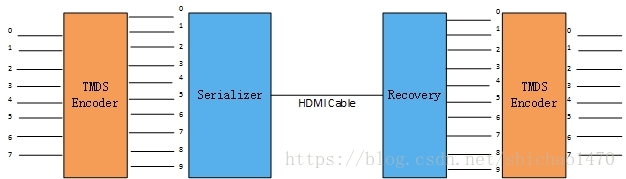

2.传输流程

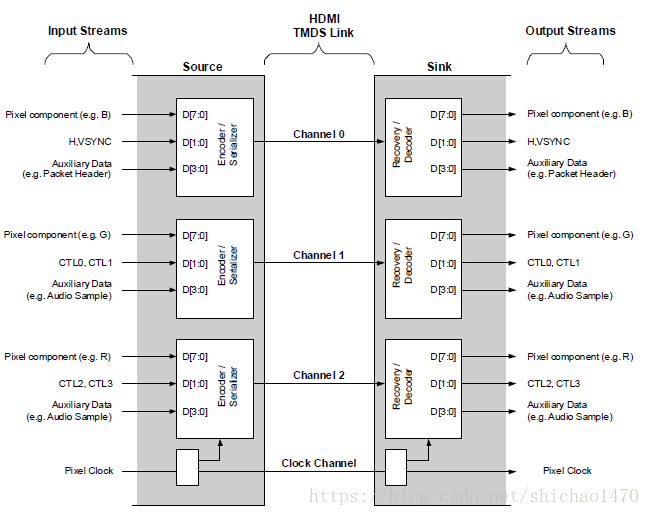

HDMI TMDS传输的数据类型有三种(加上Hsync与Vsync就算4种): Preamble(控制信息),主要用于控制接下来传输的数据是Data Island或者Video Data Data Island(数据包),各种类型的包信息,包括音频数据包,图像信息包等 Video Data (视频信息),视频像素数据,HDMI可以传输RGB与YUV两种格式的像素数据 还有Hsync与Vsync HDMI的数据传输有TMDS0,TMDS1,TMDS2三个通道,每个通道的传输流程都是一样的:

如果是8bit的数据进入TMDS编码器,得到抗干扰性强的10bit TMDS信号,然后再进行串行化输出;在接收端收到串行的HDMI信号后,进行信号复原,得到10bit的TMDS信号,最后用TMDS解码器解码得到原来的8bit数据。

3.TMDS部分

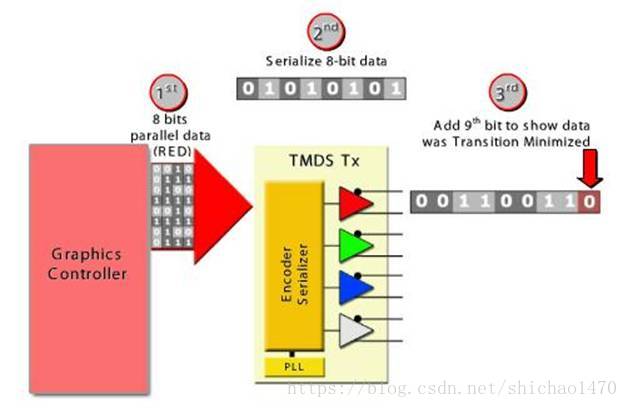

一般来说,HDMI传输癿编码格式中要包括视频数据、控制数据和数据包(数据包中包括音频数据和附加信息数据,例如纠错码等)。TMDS每个通道在传输时要包含一个2bit的控制数据、8bit的视频数据戒者4bit的数据包即可。在HDMI信息传输过程中,可以分为三个阶段:视频数据传输周期、控制数据传输周期和数据岛传输周期,分别对应上述的三种数据类型。 下面介绍TMDS中采用的技术:

1.传输最小化 以单个通道的8位数据为例,8位数据经过编码和直流平衡得到10位最小化数据,这仿佛增加了冗余位,对传输链路的带宽要求更高,但事实上,通过这种算法得到的10位数据在更长的同轴电缆中传输的可靠性增强了。下图是一个例子,说明对一个8位癿并行RED数据编码、并/串转换。

第一步:将8位并行RED数据传送到TMDS发送端。

第二步:并/串转换.

第三步:进行最小化传输处理,加上第9位,即编码过程。第9位数据称为编 码位。

2.直流平衡 直流平衡(DC-balanced)就是指在编码过程中保证信道中直流偏移为零。方法是在原本的9位数据的后面加上第10位数据,返样,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的可靠性。

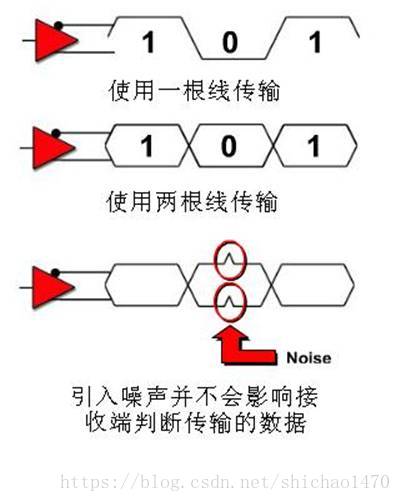

3.差分信号 TMDS差分传输技术是一种刟用2个引脚间电压差来传送信号癿技术。传输数据的数值(“0”或者“1”)由两脚间电压正负极性和大小决定。即,采用2根线来传输信号,一根线上传输原来的信号,另一根线上传输与原来信号相反的信号。这样接收端就可以通过让一根线上的信号减去另一根线上的信号的方式来屏蔽电磁干扰,从而得到正确的信号。 如下图所示:

总体传输流程如下:

如果传输的是Video Data,并且格式为RGB,那么会占用三个通道的所有24bit输入,Channel0[7:0]用于传输B,Channel1[7:0]用于传输G,Channel2[7:0]用于传输R。

如果传输的是Data Island,则占用三个通道共10bit输入,Channel0[3:2]用于传输Data Island Header(包头),Channel1[0:3]与Channel2[0:3]用于传输Data Island Content(包内数据)。

如果传输的是Preamble,则占用1,2两个通道共4bit输入,Channel1[1:0]与Channel2[1:0]分别为CTL0,CTL1,CTL2,CTL3,用于判断接下来输入的是Video Data或者Data Island

对于Hsync与VSync,会占用Channel0通道的两个bit输入,Channel0[0]为Hsync,Channel0[1]为Vsync

4.传输周期

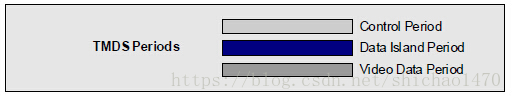

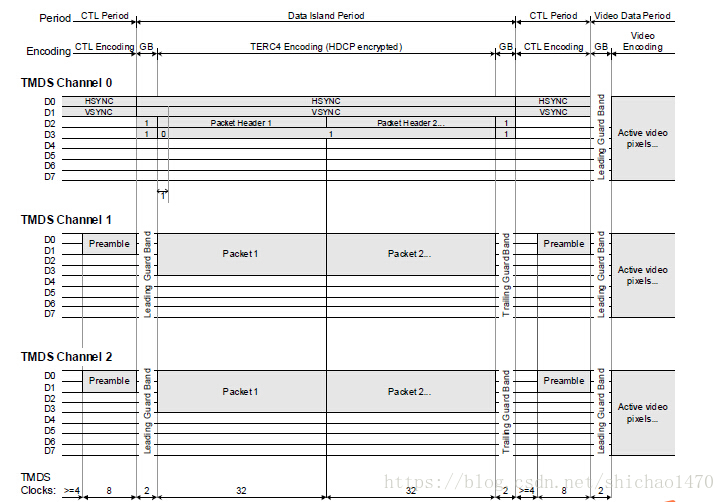

HDMI的TMDS数据传输可以分为三个传输周期:

Control Period期间会传输Hsync,Vsync,并且在该时期的最后阶段会传输Preamble

Data Island Period期间会传输Data Island(数据包),也会有Hsync与Vsync

Video Data Period期间会传输Video Data(视频像素数据)

某帧的总体周期如下:

三个传输周期的过渡如下:

左边是Control Period,传输有Hsync,Vsync与Preamble

中间是Data Island Period,传输有Hsync,Vsync,以及两个Packet Header与Packet(每32个clock 一个packet);另外Data Island的两端会用Guard Band保护并隔开Data Island的数据,因为这个阶段传输的数据大多是非常重要的,比如其中就有图像分辨率,决定后面的Video Data数据的显示方式

右边是Video Data Island,传输视频像素数据,在该时期的开头也有Guard Band

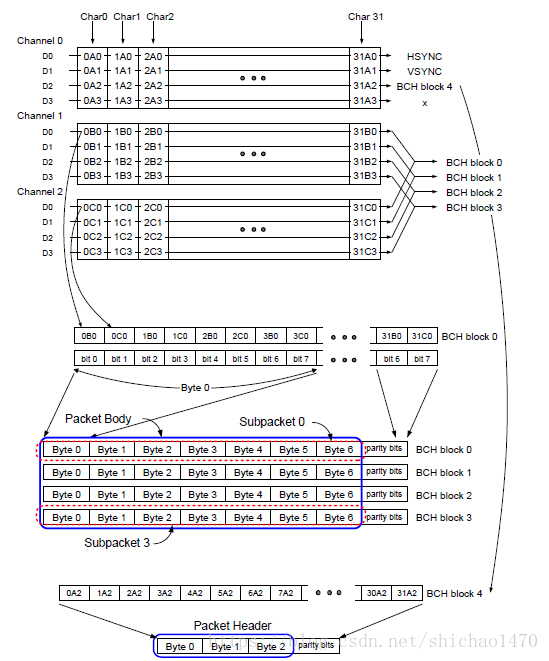

5.Data Island Packet结构

所有Data Island Packet都以32个时钟脉冲为一个周期,也就是说每32 clk传输一个包。

以上图为例,

包头部是BCH block 4,由Channel0[2]传输,32clk表示有32bit,则为4byte,前三个byte为包头,最后一byte为校验码

包体为BCH block 0,1,2,3,分别由Channel1,Channel2共8根线传输,共有24byte与6byte的校验码

Parity Bits校验码是用于检验HDMI Cable传输过程中是否发生了错误,如果该Packet在HDMI接收端校验错误,如果只有一个bit的错误,那么可以修正,超过1bit的错误会被判别为无效Packet(由于HDMI是一直在发送数据因此无法重发错误Packet?) 所以说,在接收端,在解完包之后,需要取出各个BCH block的Parity bit,进行Calibration(校验) Packet类型各种各样,详细请看HDMI Spec

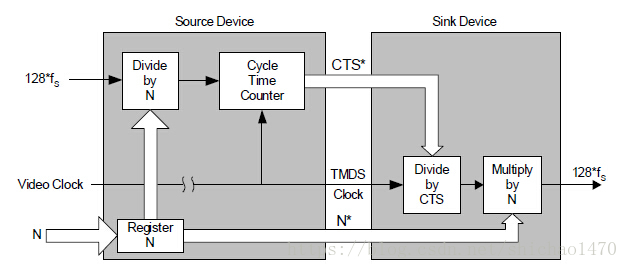

6.Audio Clock

Audio的采样率有44100,48000,192000等,是各种各样,在HDMI传输时,Audio是PCM级(无压缩)传输,把PCM数据打散到各个包内,为了得到每个音频帧的数据,也需要知道Audio的采样率。HDMI中规定Audio的传输方式:

Audio采样率fs重建依靠的主要参数为:

TMDS Clock

CTS

N

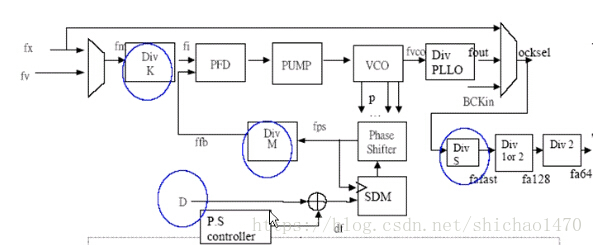

在发送设备这端,已知参数有采样率fs,视频时钟Video Clock(TMDS clock),以及预先设定好的参数N,求CTS: CTS=N∗f TMDS 128×f x CTS=N∗fTMDS128×fx CTS = \frac{N *f_{TMDS}}{128\times{f_x}} 在接收设备这端,TMDS clock通过硬件设备可以得到,N,与CTS通过Audio Packet传输过来,求fs: 128∗f s =N×f TMDS CTS 128∗fs=N×fTMDSCTS 128*f_s = \frac{N\times{f_{TMDS}}}{CTS} 在接收端为了保持fs的稳定与精确,需要进行锁相,即用VCO(Voltage-controlled oscillator压控振荡器,通过电压控制产生的频率)产生合适的频率,然后用PFD(Phase Frequency Detector)来锁频

首先,由于VCO有个最佳的工作区域如(200MHz~500MHz),那么为了保证VCO在最佳工作频率内,我们可以从后倒推回来,先对输出的fa128做乘法得到

f vco =f a128 ×S×S 2 fvco=fa128×S×S2 f_{vco} = {f_{a128}}\times{S}\times{S_2}

由于f a128 fa128 f_{a128} 只有那么几种(44.1k,48k等),所以比较容易得到S S S 与S 2 S2 S_2

然后,为了更快进行频率匹配,需要对近来的频率f x fx(就是晶振时钟f crystal fcrystal)或者f v fv(pixel clock)做除法,也对f vco fvco做除法,令两个趋向相等。对于细微的区别可以用D Code 进行修正

f vco M =f x K fvcoM=fxK \frac{f_{vco}}{M} = \frac{f_x}{K}

最后做PFD锁相 第2,3步的反馈操作循环地进行,最后可以得出比较稳定的f vco fvco 最终得到

f a128 =f vco S×S 2 fa128=fvcoS×S2 f_{a128} = \frac{f_{vco}}{{S}\times{S_2}}

7.HotPlug

HotPlug即热拔插,当接上接口时就可以判定设备是否存在,以进行后续工作。

HDMI source device(HDMI HPD)会监测sink device的Hotplug端口,如果Hotplug为High,则证明设备可以工作,然后去读取DCC,如果为low,则证明设备已断开。

HDMI sink device应该通过把Hotplug拉低,来通知source device EDID已经被改变,那么source device在Hotplug被拉高后,就会重新来读取新的EDID,拉低这段时间应该多于100ms。

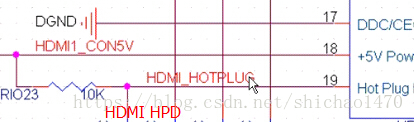

HDMI规定,HDMI 的5v引脚通电时,可以通过DCC去读取EDID,即需要保证Hotplug为high,有些Hotplug是直接接到5V上的(如下)。 Hotplug接法:(HDMI HPD(Hotplug detect ?)检测sink的Hotplug端)

上面用5V引脚进行供电,并接上Hotplug,这样做就能保证每次source device接上sink device时,都可以去读取到EDID。但是这样做有一个缺点,当5V电源断开时,会有5v的电压回灌给HDMI HPD与Hotplug,5V电压会冲击Hotplug,一旦Hotplug引脚无法承受5V电压的回灌,会被打穿。

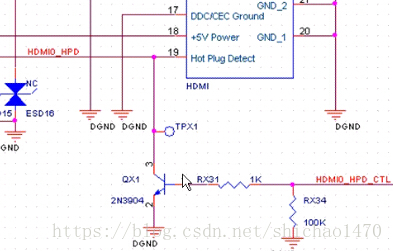

下面有个较好的Hotplug接法:

上面用的是额外的GPIO引脚加上三极管控制HDMI HPD为0还是1,如果HDMI0_HPD_CTL输出0,那么三极管断开,HDMI0_HPD侦测到High,如果HDMI0_HPD_CTL输出1,那么三极管打通,HDMI0_HPD侦测到low。

8.HDMI Sink

例如像TV这种就是HDMI的接收端,那么HDMI接收端需要做些什么东西。

HDMI可以接收到的有三个通道的TMDS Data,TMDS Clock,可以设置Hotplug,还有DCC传输用的I2C引脚。上面已经讲了TMDS Data,与设置Hotplug,接下来分析TMDS Clock。

TMDS Clock 就是Pixel Clock,即一个像素点所用的时钟频率。TMDS Clock通过clk 引脚传输到接收端,但是接收端并不清楚发送端发过来的TMDS Clock 频率为多少,因此需要通过Phy(PHY是模拟数字转换部分,不同于ADC,PHY是不知道采样频率的,需要自己锁频、锁相,侦测确切的输入频率)来进行锁相得到。但是由于HDMI频宽太宽(480P@60Hz为25.2MHz,1080P@60Hz为162MHz,甚至还有高达340MHz的),一般VCO(压控振荡器,通过电压控制产生的频率)无法覆盖这么大的范围,因此需要分频带来设置Phy:

先侦测输入频率落在哪个频带,然后根据不同频带做不同设置。

用TV产生的晶振来数count,数得count后就知道TDMS Clock了

f crystal =count×f TMDS fcrystal=count×fTMDS f_{crystal} = {count}\times{f_{TMDS}} ??

或者用1024个TMDS Clock来数晶振个数

1024×f TMDS =count×f crystal 1024×fTMDS=count×fcrystal {1024}\times{f_{TMDS}} = {count}\times{f_{crystal}} ??

由于视频信号从RGB个8bit通过TMDS编码后变成了10bit,然后又串行化,所以实际用于接收TMDS Data所用的时钟应该为: f ReceiveClock =10×f TMDS fReceiveClock=10×fTMDS f_{ReceiveClock} = {10}\times{f_{TMDS}}

另外ReceiveClock也可以不用直接采用上面的乘法,而是采用TMDSClock为参考、硬件锁相的方法来得到。 得到ReceiveClock后就可以去设置频率PLL,然后对三个通道进行采样得到TMDS Data。

9.Timming Detect

在Sink端还有需要进行Timming Detect,因为如果设备可以支持(如chroma),HDMI可以自由更换Timming,而当Timming更换了之后,Sink需要重新设定Phy。因此,通过侦测频率的改变来检测是否更换了Timing是必要的。一般会有一个中断服务(或循环)线程来侦测频率的改变,一旦频率改变后,该进程会通知重新设定Phy,保证HDMI的正确运行